台积电在2023年报里指出,台积电的2nm研发着重于基础制程制定、良率精进、电晶体及导线效能改善以及可靠性评估,预计2024年内,重要客户完成芯片设计,并开始做验证。

英特尔是副总裁在采访中表示,英特尔的20A即2nm工艺将在2024年进入量产,而英特尔准备再次引领小型化,其中Arrow Lake是主导产品,预计将于2024年下半年推出。

三星呢,则是在财报中表示,其代工厂将在6月正式推出SF2即2nm工艺,SF2的PDK、EDA 工具和授权 IP)将在2024年第二季度完成,随后合作伙伴就能使用SF2来设计制造芯片。

三大代工厂都把2nm的推出当成是一场重头戏,但目前我们仍然心存疑问:2nm到底能用来干什么?它能在多大程度上改变目前的芯片?

最近,台积电执行副总裁兼联席首席运营官米玉杰与AMD首席技术官马克·佩珀马斯特 (Mark Papermaster)展开了有关于2nm的对话,这或许能帮助我们对2nm以及之后的世界有一个更深入的理解。

物理和创新的界限

在这次谈话中,台积电首席运营官米玉杰首先提到了2nm的艰难,台积电从0.5微米开始到2nm,在三十余年的时间里,晶体管的缩放超过了4000倍,但随着制程的升级,扩展也变得越来越有挑战性,但他认为,2nm之后仍然有发展空间,成功关键就是客户合作。

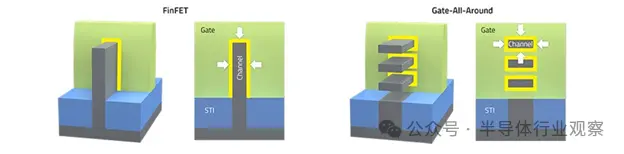

米玉杰表示,先进制成的进化还未停止,机会和挑战机会并存,台积电采用双研发团队体制,通过两支团队交替推出最新制程,拥有更多时间和技术资源,虽然目前每代制程开发周期长达五年甚至七年,较之前二至三年明显放缓,但未停止。他强调,7nm制程之后,台积电每一个新制程都会导入新技术,2nm将导入更复杂的GAAFET技术,暂定2025 年量产。

他也提到,台积电正在开发技术,包括硅光子技术、与 DRAM 供应商合作来优化HBM,以及研究将n和p两种MOS器件相互堆叠在一起的CFET晶体管方案等。台积电未来还会进行更多开发,以推动半导体业继续向前。

而AMD的首席技术官佩珀马斯特也对目前先进制程提出了自己的看法,他表示,2010 年代初以来,传统代工厂和无晶圆厂IC 设计企业合作模式逐渐显露不足,在现在的代工市场中,甲乙方需要达成更密切的合作,大家一同努力来让芯片发挥应有的性能。

佩珀马斯特认为,台积电所强调的设计制程协同最佳化(DTCO,Design-Technology Co-Optimization)作用越来越大。一方面DTCO 有助辨识过于极端而缺乏价值的制程路线,聚焦客户真实需求,减少开发压力,另一方面,DTCO 可帮助客户产品性能、能耗、芯片面积三大要素间取得平衡,达成单纯制程微缩难实现的目标。DTCO 也有助发挥单一节点的技术潜力。

佩珀马斯特所提到的DTCO,可能有很多人对它还不够了解,这项神秘方法,在台积电在过去几个世代先进制程的效能提升方面扮演了重要角色。

DTCO即设计技术协同优化,如其字面所示,就是设计与制程技术寻求整合式的优化,来改善效能、功耗效率、电晶体密度、以及成本,台积电此前曾表示,制程研发团队与设计研发团队一开始就必须携手合作,针对下一世代技术的定义进行设计技术协同优化,两个团队必须保持开放的心态,探索设计创新与制程能力的可能性,许多创新的想法都在这个阶段被提出来,其中有些想法可能太积极而无法借由既有技术实现,有些想法初步看起来可能很有潜力,但是结果却没那么实用,而设计技术协同优化的目的就在于定义真正有意义的调整,超越单纯的几何微缩,进而达成提升效能、功耗、面积的目标。

举例来说,台积电的7nm就是设计技术协同优化成功的证明之一。其在16nm率先采用鳍式场效(FinFET)晶体管结构时,采用三鳍结构于单一标准元件,提供优于平面式电晶体的驱动强度。基于鳍式分离的特性,第一代FinFET技术使用通用型鳍式栅格(global fin grid)将鳍的置放弹性最大化,此类型栅格预先设定好鳍的放置位置,是一种应用在整个芯片上支持逻辑及混合新号设计的通用鳍式栅格系统。

迈入到7nm时,台积电发现通用型鳍式栅格也许不是优化效能、功耗、面积的最佳选择,因此在进行设计技术协同优化探索时推出特殊型鳍式栅格(local fin grid)的概念,创造了优化标准元件鳍片置放的灵活性,并将寄生电容和电阻降到最低。如此一来,相较于前一世代制程,我们能够使用更少的鳍数量来达到所需的效能,同时提升密度。相较于10nm制程,DTCO让台积电的7nm制程逻辑密度增加超过1.6倍,速度增快约20%,功耗降低约40%。

DTCO从整体角度审视设备如何相互交互以及它们如何同时满足多种要求,并促使代工厂寻找构建设备的新方法,它成为了从平面晶体管过渡到 finFET 晶体管的关键因素,而从 finFET 中汲取的工程经验成为了全栅纳米片晶体管以及未来叉片晶体管和 CFET 的推动者。

当传统的扩展方法开始力不从心时,DTCO 才真正开始受到重视。通过共同优化设计与技术、系统与技术,系统架构师可以从技术中获得比传统扩展方法更多的优势,孤立的设计和工艺步骤需要发展成为跨职能团队,广泛的合作已被认为是推动半导体发展的关键,伴随着GAA的推出,DTCO的重要性愈发凸显。

佩珀马斯特作为芯片设计公司的技术人员,与来自晶圆代工厂的米玉杰在这一方面达成了共识:2nm乃至更先进的制程,不再是晶圆代工厂的闭门造车,而是需要更多设计公司的助力,伴随制程的不断推进,代工厂和设计公司也结合得愈发紧密,多方合作来延续摩尔定律。

来自Chiplet的助力

对于2nm之后的芯片技术,AMD也在另一段视频中提出了新的观点,AMD首席技术官佩珀马斯特与AMD 高级副总裁兼企业研究员萨姆·纳夫齐格(Sam Naffziger)讨论了Chiplet,如何将半导体分解成以新颖的方式组装在一起的组件,并以此挑战摩尔定律的放缓,或许也可以为2nm乃至之后的半导体业界提供助力。

佩珀马斯特和纳夫齐格都强调了芯片标准化的重要性。

“特定领域的加速器,是实现每瓦每美元最佳性能的最佳途径。因此,这对于取得进步绝对是至关重要的,”纳夫齐格解释说,“你不可能为每一个领域都提供特定的产品,所以我们能做的是建立一个芯片生态系统——本质上是一个库。”

纳夫齐格指的是通用芯片组互连 Express(UCIe)——一种芯片组通信的开放标准,该标准自 2022 年初创立以来,已经赢得了包括 AMD、Arm、英特尔和英伟达在内的巨头广泛支持,不少中小型企业也在尝试接入这一标准。

AMD 自 2017 年推出第一代 Ryzen 和 Epyc 处理器以来,一直走在芯片组架构的前沿。如今,Zen的芯片库已经发展到包括多个计算、I/O 和图形芯片,并将其组合打包到消费级和数据中心处理器中。而AMD 于 2023 年 12 月推出的 Instinct MI300A APU 就是芯片组的实例之一,它包含 13 个独立的芯片——4 个 I/O 芯片、6 个 GPU 芯片和 3 个 CPU 芯片,以及 8 组 HBM3 内存。

纳夫齐格表示,在未来,像UCIe这样的标准可能会让第三方制造的芯片组进入AMD的封装中,他提到了硅光子互连,这种可以缓解带宽瓶颈的技术,在未来有可能将第三方芯片带入 AMD 产品。不过他也认为,如果没有低功耗的芯片到芯片互连技术,硅光子互连是不可行的。

纳夫齐格说:“你将光学技术安装在芯片上,是因为你需要巨大的带宽。因此你需要每比特的相对低能耗,这样才有意义,而封装内芯片是获得低能耗接口的途径。"他认为向共同封装光学技术的转变“即将到来”。

为此,几家硅光子初创公司已经在推出这样的产品。例如,Ayar 实验室开发了一种兼容 UCIe 的光子芯片组,该芯片组已集成到英特尔去年制造的图形分析加速器原型中,不过截至目前,第三方芯片(无论是光子芯片还是其他芯片)还没有正式进入到 AMD 产品中,有待进一步的发展,要实现异构多芯片,标准化只是需要克服的众多挑战之一。

值得一提的是,AMD 曾经向竞争对手的芯片制造商提供过芯片组,英特尔在 2017 年推出的 Kaby Lake-G 部件采用了 Chipzilla 的第八代内核和 AMD 的 RX Vega GPU,该部件最近又出现在 Topton 的 NAS 板上。

纳夫齐格此前还接受过IEEE Spectrum的采访,在关于Chiplet如何改变半导体制造工艺这一问题上,他也发表了自己的看法。

“这绝对是该行业正在努力解决的问题。这就是我们今天所处的位置,也是我们 5 到 10 年后可能发展的方向。我认为现在的技术基本上都是通用型的,它们可以很好地与单片芯片相匹配,也可以用于芯片组。对于芯片,我们拥有更专业的知识产权。因此,我们可以设想在未来实现工艺技术的专业化,并获得性能优势、成本降低和其他方面的好处。但这并不是目前的产业现状。” 纳夫齐格说到。

纳夫齐格表示,AMD架构的目标之一是让它对软件完全透明,目前AMD正在想方设法扩展逻辑功能,但 SRAM 是一个更大的挑战,而模拟功能肯定无法扩展。AMD已经采取了将模拟与中央 I/O 芯片分离的措施,如3D V-Cache——一种与计算芯片三维集成的高密度缓存芯片,他希望未来会有更多这样的专用化产品。

在摩尔定律放缓的如今,Chiplet能帮助AMD实现更多技术上的愿景,即便是制程推进至2nm之后,Chiplet也能帮助解决SRAM这样的痛点,截至目前,标准化是Chiplet亟需解决的一个问题。

写在最后

2nm的争夺战目前已经悄然展开,台积电、英特尔和三星开始寻找自己的客户,数以百亿计的美元砸向了新的晶圆厂,第一个大规模量产2nm芯片的厂商,无疑会引领之后的工艺制程革命。

但对于AMD这样的无晶圆厂公司来说,2nm这样的昂贵的先进制程,不是单纯的提升芯片的晶体管密度,还要顾及未来的架构演进,以及先进封装等技术的交汇融合,如何权衡2nm乃至1.6nm的工艺,又给未来的芯片设计行业提出了新难题。

【来源:半导体行业观察】