11月21日,2025集成电路发展论坛(成渝)暨第三十一届集成电路设计业展览会(以下简称:ICCAD-Expo 2025)在成都西部国际博览城盛大闭幕。

这场汇聚 300 余家行业领军企业、超万名专业观众的技术盛宴上,国内领先的高速接口 IP 及解决方案提供商晟联科成为全场焦点:不仅首次公开展示 PCIe PHY+Controller 一体化方案,CEO 陈继强更是受邀参与【IP与IC服务设计分论坛】,发表主题为《3D Interface IP,新一代架构算力芯片的互联基石》的演讲,全方位分享晟联科在边缘算力互联领域的技术突破与产业落地成果。

▲ 晟联科创始人&CEO 陈继强

主题演讲:3D Interface IP,筑牢算力芯片底层基石

随着高性能计算正在经历一场新的革命,大模型推理推动算力竞争从通用芯片转向专用芯片。3D堆叠突破内部带宽后,芯片堆叠之间互联设计却成了新的瓶颈。

陈继强首先介绍了晟联科3D接口IP的技术成果,晟联科的互联方案让专用芯片客户无需攻克数模混合设计的难题,就能构建Tbps级数据航道。这不仅是接口技术的进步,更是让3D IC真正释放澎湃算力的互联基石!

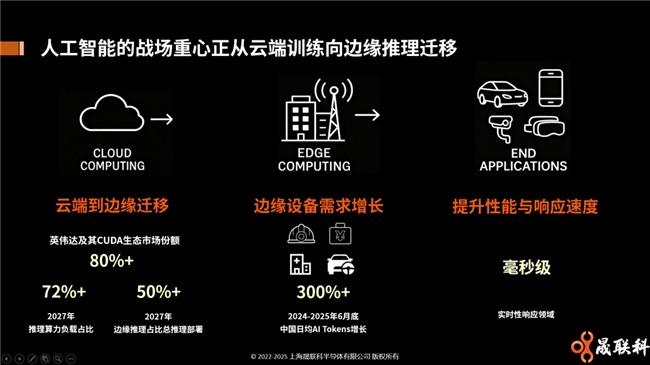

他表示,随着AI 产业竞争重心正从云端训练向边缘推理快速迁移。数据显示,到 2027 年推理算力负载占比逼近 80%,其中边缘推理部署占比达 50% 以上,自动驾驶、智能工厂、AI 手机等场景的规模化落地,推动高效、可扩展、成本最优的推理算力成为产业发展新引擎。

面对边缘场景对高速推理、高可靠性、低成本功耗的三重核心诉求,传统架构难以突破 "内存墙" 瓶颈。在典型推理任务中,存储的带宽的利用率不到50%,计算在等存储。而存算一体架构通过将计算单元嵌入存储阵列,从根本上减少数据搬运,可将算力利用率提升 20% 以上,成为破解边缘推理困境的关键技术路径。

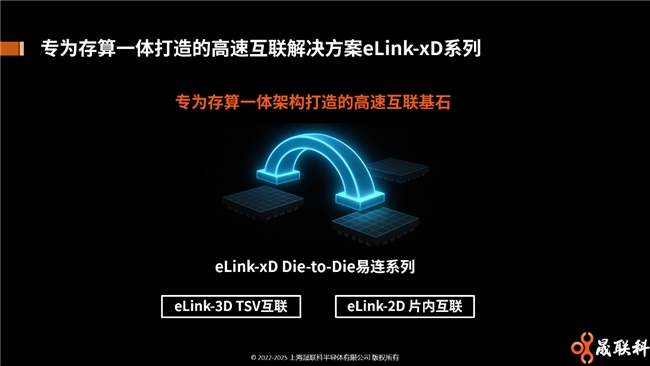

01技术破局:eLink-xD 系列突破TSV互联瓶颈

陈继强强调,存算一体架构虽打破 "内存墙",却面临 3D 堆叠带来的互联设计复杂性新瓶颈,TSV 互联质量直接决定系统最终性能。为此,晟联科针对性打造 eLink 系列高速互联解决方案技术矩阵:eLink-xD 系列提供先进 Die-to-Die 连接能力,eLink-2D 解决片内互联挑战,eLink-3D 突破 TSV 互联瓶颈。

02落地实力:从系统级封装到全场景适配,解决大规模芯片设计的时序收敛难题

从架构到实体落地,eLink-xD 已实现系统级封装(SiP)的成熟应用,兼容 Logic-on-Memory、Logic-on-IO、Memory-on-Logic 混合堆叠三种主流 3D IO 实现形态,适配 HBM、异构集成等多样化场景。其内置链路训练、时延锁定、温度自适应机制,实现超越 1E-15 的 BER 可靠性,可从容应对高低温、强干扰等严苛环境。

03 3D布局:更高性能,助力多应用高速互联

演讲最后,陈继强公布晟联科 3DIO 技术研发路径图:现阶段聚焦成熟工艺下的可靠性通信设计,未来利用更先进工艺节点进行功能迭代,进一步提升带宽、带宽密度与能效,从而覆盖更多场景。

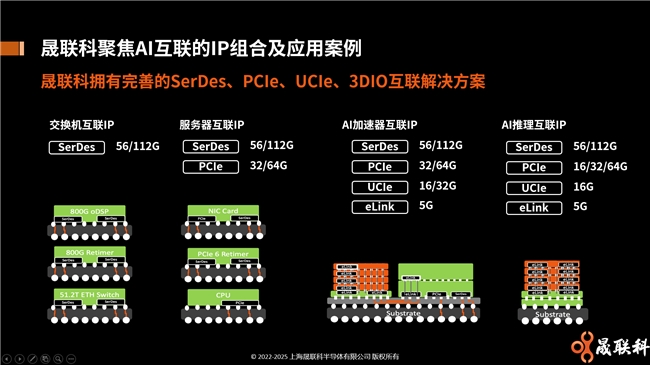

同时,晟联科已构建包含 56G/112G SerDes、PCIe 6.0、UCIe、3D IO 的完整高速IP互联技术矩阵,累计赋能客户超 100 亿美元设备出货,成为全球芯片企业可靠的互联技术伙伴。

晟联科精彩直击: PCIe PHY+Controller 方案首秀

此次ICCAD-Expo 2025展会上,晟联科D83、D84 展台人气爆棚,三大高速接口 IP 解决方案集中亮相,成为专业观众驻足交流的核心区域。

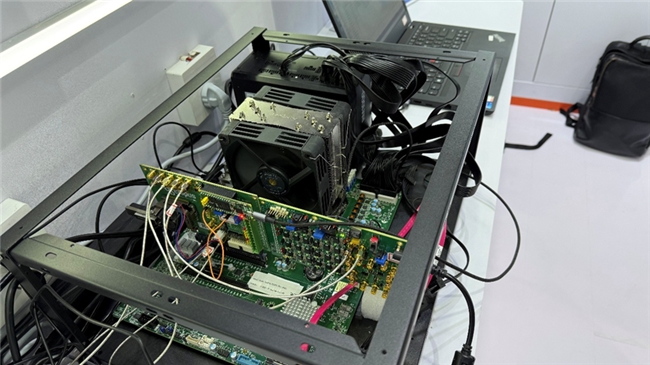

01 重磅首发:PCIe PHY+Controller 方案实现高速互通实测

展台上,晟联科重点展示了PCIe PHY+Controller 全栈方案引发行业广泛关注,现场完成两大关键实测验证:

· 实现PCIe 5 应用<-> Transaction Layer <-> Physical Layer的高速互通测试;

· 实现晟联科PCIe测试板与商用Server CPU的高速互通测试。

该方案通过物理层(PHY)与控制器(Controller)的 集成,无需额外适配即可快速部署,大幅降低客户集成成本与研发周期。其全面兼容 PCIe Gen1-Gen5 规范,覆盖2.5GT/s 至 32GT/s 速率,可灵活匹配边缘智能、高性能计算等多场景需求,为设备提供稳定高效的高速互联支撑,精准契合大算力时代的技术刚需。

▲ 现场观众观看PCIe Demo

以技术为核心,赋能算力生态新发展

从 PCIe PHY+Controller 一体化方案的实测落地,到 eLink-xD 系列解决方案的全场景适配,再到 3DIO 技术的未来布局,晟联科正以 "系统级互联伙伴" 的定位,持续破解算力互联瓶颈,为边缘计算、AI 推理等领域提供核心技术支撑,助力中国集成电路产业链高质量发展。

未来,晟联科将继续深耕高速接口 IP 技术研发,推动更多创新方案落地应用,与行业伙伴携手构建共赢的算力互联生态!